Chiplet-Innovationen für Europa: Startschuss für APECS-Pilotlinie im Rahmen des EU Chips Acts

Die Pilotlinie für »Advanced Packaging and Heterogeneous Integration for Electronic Components and Systems« (kurz APECS) ist ein wichtiger Baustein des EU Chips Act, um Chiplet-Innovationen voranzutreiben und die Forschungs- und Fertigungskapazitäten für Halbleiter in Europa zu erhöhen. Die in der Forschungsfabrik Mikroelektronik Deutschland (FMD) kooperierenden Institute arbeiten eng mit weiteren europäischen Partnern am Aufbau der APECS-Pilotlinie und leisten damit maßgeblich einen Beitrag, Europas technologische Resilienz zu stärken und somit auch die globale Wettbewerbsfähigkeit in der Halbleiterindustrie zu steigern. Sowohl großen Industrieunternehmen als auch KMU und Start-ups wird die Pilotlinie einen niederschwelligen Zugang zu Cutting Edge-Technologien ermöglichen und für sichere, resiliente Halbleiterwertschöpfungsketten sorgen. Das Fraunhofer IAF beteiligt sich an APECS mit der Entwicklung neuartiger InGaAs-auf-Si- und GaN-auf-SiC-Chiplets für Hochfrequenzanwendungen sowie Microbump-Interposer. APECS wird durch Chips Joint Undertaking und durch nationale Förderungen von Belgien, Deutschland, Finnland, Frankreich, Griechenland, Österreich, Portugal und Spanien im Rahmen der »Chips for Europe« Initiative kofinanziert. Die Gesamtfinanzierung für die APECS-Pilotlinie beläuft sich auf 730 Millionen Euro über 4,5 Jahre.

Europa verfügt über ein dynamisches Ökosystem aus führenden Unternehmen in traditionellen Branchen, kleinen und mittleren Unternehmen (KMU) sowie Start-ups, deren Wettbewerbsvorteil auch auf fortschrittlichen Halbleiterlösungen, die die Basis für Innovationen bilden, beruht. Diese Unternehmen stehen heute jedoch vor der Herausforderung, dass der Zugang zu fortschrittlichen Technologien aufgrund fehlender Ressourcen in Europa begrenzt ist. Die Europäische Kommission investiert im Rahmen des EU Chips Acts erhebliche Mittel in die Stärkung von Halbleitertechnologien und -anwendungen in der EU. Damit sollen die technologische Resilienz Europas erhöht, Liefer- und Wertschöpfungsketten gesichert und Innovationen in Schlüsselbranchen, wie Künstliche Intelligenz, Mobilität, Produktion, Informations- und Kommunikationstechnologien, vertrauenswürdige und ökologisch nachhaltige Elektronik sowie neuromorphes- und Quantencomputing vorangetrieben werden.

Die APECS-Pilotlinie setzt hier beim skalierbaren Industrietransfer neu entwickelter Innovationen im Bereich Heterointegration*, insbesondere beim Einsatz neuer Chiplet**-Technologien an und schlägt so die Brücke zur anwendungsorientierten Forschung. APECS geht über herkömmliche »System-in-Package-Methoden« (SiP) hinaus und zielt darauf ab, robuste und vertrauenswürdige heterogene Systeme zu liefern, die die Innovationsfähigkeit der europäischen Halbleiterindustrie erheblich steigern.

Investitionen in strategische Projekte wie APECS im Rahmen des EU Chips Acts sind von entscheidender Bedeutung, um Europa als unverzichtbaren Partner in der globalen Technologiebranche zu positionieren. Deutschland nimmt in diesem Bestreben eine Schlüsselrolle ein – sowohl als führender Forschungsstandort als auch als treibende Wirtschaftskraft. Dank der erheblichen Förderung durch das Bundesministerium für Bildung und Forschung (BMBF) und der Bundesländer Sachsen, Berlin, Bayern, Schleswig-Holstein, Baden-Württemberg, Nordrhein-Westfalen, Brandenburg und Sachsen-Anhalt ist es in den kommenden Jahren möglich, die FuE-Infrastruktur im Rahmen der APECS-Pilotlinie weiter auszubauen. Dies ist ein wichtiger Schritt, um die langfristige wirtschaftliche Stabilität Deutschlands und Europas zu sichern.

»Fraunhofer spielt eine zentrale Rolle bei der Umsetzung von Großprojekten wie APECS, die die Innovationskraft und technologische Resilienz Deutschlands stärken«, betont Prof. Holger Hanselka, Präsident der Fraunhofer-Gesellschaft. »Durch unsere praxisnahe Forschung und die enge Zusammenarbeit mit Industrie, Wissenschaft und politischen Partnern schaffen wir die Grundlage, um neueste Technologien nicht nur zu entwickeln, sondern auch in die industrielle Anwendung zu bringen. Die APECS-Pilotlinie steht exemplarisch für den Brückenschlag zwischen Forschung und Wirtschaft und unterstreicht, wie eine enge Kooperation mit Ministerien und anderen Partnern die Stellung von Europa am globalen Mikroelektronikmarkt nachhaltig sichern kann.«

Innovationen genau dort, wo die europäische Industrie sie am dringendsten benötigt

Die APECS-Pilotlinie zielt darauf ab, neue Funktionalitäten durch die sogenannte »System Technology Co-Optimization« (STCO) zu aktivieren und Integrationstechnologien zu vereinheitlichen. Dies wird es Unternehmen ermöglichen, fortschrittliche Produkte auch in kleinen Stückzahlen zu wettbewerbsfähigen Kosten zu entwickeln. Durch die Bereitstellung einer Vielzahl von Technologien in einem One-Stop-Shop wird APECS zukünftig Europas führender Hub für Advanced Packaging und Heterointegration und nimmt damit eine entscheidende Schlüsselrolle für die europäische Mikroelektronik ein.

Als treibende Kraft für die Zusammenarbeit zwischen europäischen Forschungseinrichtungen, Industrie und universitärer Forschung fördert die APECS-Pilotlinie ein lebendiges Innovationsökosystem. Als umfassende Plattform integriert APECS ein end-to-end Design sowie Pilotproduktions-kapazitäten und ermöglicht so die Weiterentwicklung von Innovationen von der Spitzenforschung zu realisierbaren, skalierbaren Fertigungsverfahren.

APECS wird eine entscheidende Rolle beim Übergang Europas zu einer klimaneutralen und kreislauforientierten Wirtschaft übernehmen, indem es Ökodesign und nachhaltige Fertigungsinitiativen vorantreibt.

Innovation durch starke Zusammenarbeit auf mehreren Ebenen

Die APECS-Pilotlinie baut auf den in der Forschungsfabrik Mikroelektronik Deutschland (FMD) geschaffenen Strukturen auf. In Deutschland sind insgesamt zwölf Institute des Fraunhofer-Verbunds Mikroelektronik sowie die zwei Leibniz-Institute FBH und IHP an APECS beteiligt. Geleitet werden die Arbeiten von der Geschäftsstelle in Berlin.

Prof. Albert Heuberger, Sprecher des Fraunhofer-Verbunds Mikroelektronik und Vorsitzender des Lenkungskreises der FMD, betont: »Der Erfolg des EU Chips Acts beruht auf starken Partnerschaften und vielseitigem Know-how. Genau das bringt die FMD mit, indem sie die Stärken von dezentral organisierten Forschungseinrichtungen miteinander verbindet. Auf diesem Fundament baut auch APECS auf und kann daher zu einer langfristig zugänglichen Pilotlinie für alle europäischen Interessengruppen über die gesamte Wertschöpfungskette hinweg werden. Zusammen mit den anderen Pilotlinien im Rahmen des EU Chips Acts ist APECS eine entscheidende Komponente für Heterointegration und Advanced Packaging einer übergeordneten pan-europäischen Mikroelektronik-Pilotlinie.«

In einem starken europäischen Konsortium bündelt APECS die technologischen Kompetenzen, Infrastrukturen und das Know-how von insgesamt zehn Partnern aus acht europäischen Ländern: Deutschland (Fraunhofer-Gesellschaft als Koordinator, FBH, IHP), Österreich (TU Graz), Finnland (VTT), Belgien (imec), Frankreich (CEA-Leti), Griechenland (FORTH), Spanien (IMB-CNM, CSIC) und Portugal (INL). Die APECS Pilotlinie wird von der Fraunhofer-Gesellschaft koordiniert und von der Forschungsfabrik Mikroelektronik Deutschland (FMD) implementiert.

Beitrag des Fraunhofer IAF: InGaAs-auf-Si- und GaN-auf-SiC-Chiplets für Hochfrequenzanwendungen

Als ein in der FMD kooperierendes Institut entwickelt das Fraunhofer IAF im Rahmen von APECS neuartige Chiplets auf Basis der hybriden Halbleitermaterialsysteme Indiumgalliumarsenid-auf-Silizium (InGaAs-auf-Si) und Galliumnitrid-auf-Siliziumcarbid (GaN-auf-SiC) sowie Microbump-Interposer. Diese Technologien eignen sich aufgrund herausragender Werte in zentralen Parametern wie Rauschen, Ausgangsleistung und Effizienz besonders gut für Hochfrequenzanwendungen und versprechen Innovationen in der Messtechnik, Kommunikation, Radartechnik und Sensorik.

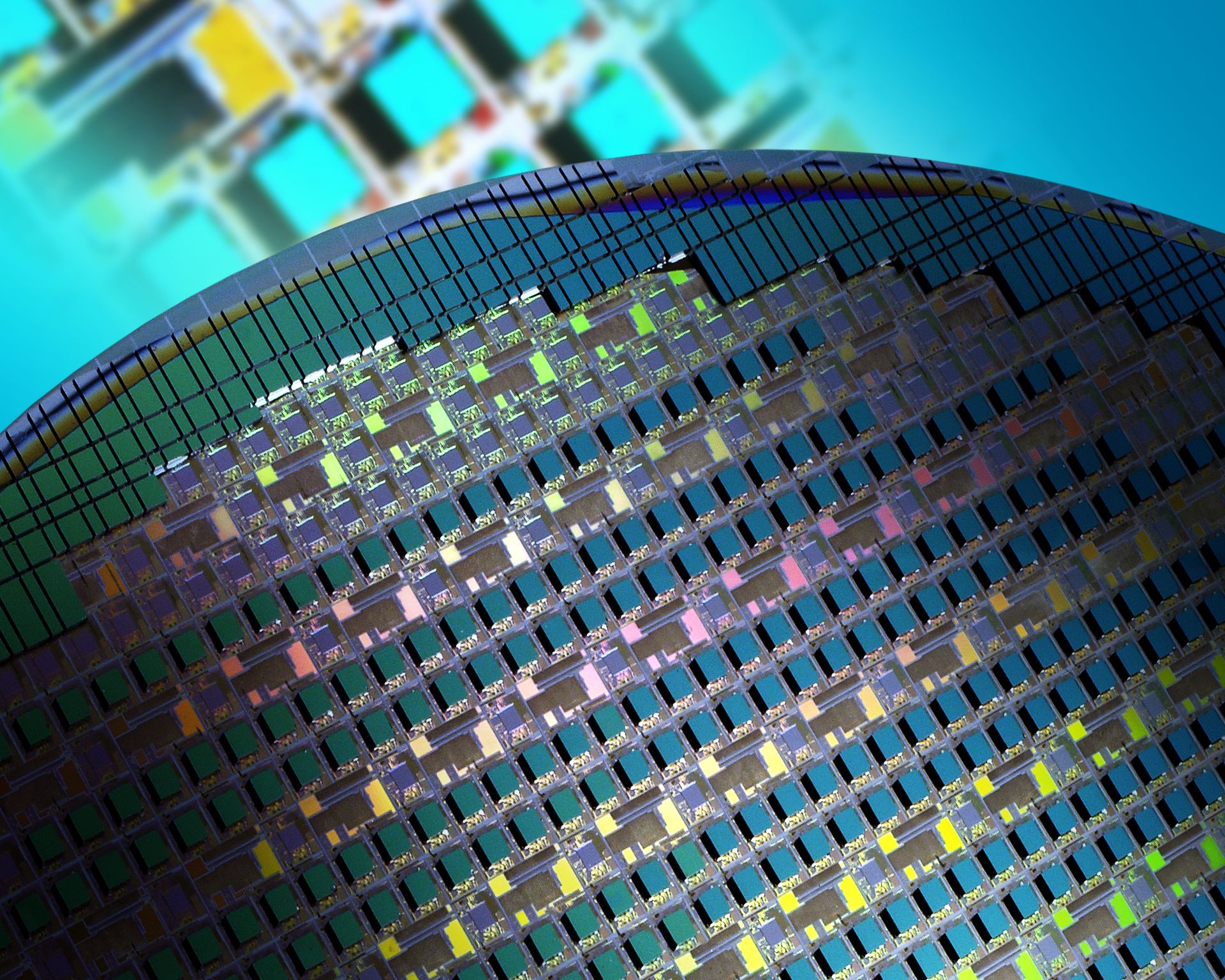

Um einen einfachen Transfer in die Industrie zu gewährleisen, sollen Entwicklung und Fertigung der Chiplets und Interposer am Fraunhofer IAF auf 6‘‘-Wafern stattfinden. Im Reinraum des Instituts werden deshalb neue Anlagen für die Bereiche Epitaxie, Prozesstechnologie und Messtechnik beschafft und in Betrieb genommen. Zudem werden bestehende Prozesse für die Chiplet- und Interposer-Fertigung angepasst.

Förderung

APECS wird vom Chips Joint Undertaking und den nationalen Finanzierungsstellen von Belgien, Deutschland, Finnland, Frankreich, Griechenland, Österreich, Portugal und Spanien im Rahmen der Initiative Chips for Europe kofinanziert.

Die Verwendung der Fotos ist ausschließlich im Zusammenhang mit dieser Pressemitteilung und unter Angabe des Copyrights gestattet.

*Über Heterointegration

Die Halbleiterforschung und -entwicklung ist das Herzstück der aktuellen technologischen (R)Evolutionen, die von Künstlicher Intelligenz und Hochleistungsrechnen über moderne Verteidigungssysteme bis hin zu Robotik, Leistungselektronik, drahtloser Kommunikation, E-Health, Quantentechnologien und mehr reichen. Solche zukünftigen elektronischen Systeme werden immer mehr Funktionen erfordern, die nicht von einem einzigen Chip geleistet werden können, selbst wenn fortschrittliche sogenannte System-on-Chip (SoC) Konzepte verwendet werden. Heterointegration wird über die aktuellen System-in-Package-Ansätze (SiP) hinausgehen und ist für elektronische Systeme und Geräte der nächsten Generation, die auf zukünftigen CMOS-Knoten, SiGe, SiC, III/Vs wie GaAs oder GaN und allen verschiedenen Arten von mikroelektromechanischen Systemen (MEMS) basieren, von entscheidender Bedeutung.

**Über Chiplets

Die Idee hinter Chiplets ist, verschiedene Arten von Intellectual Property (IP) zu verwenden, die für bestimmte Funktionen genutzt werden können. Unter IP-Cores wird ein vielfach einsetzbarer, vorgefertigter Funktionsblock eines Chipdesigns in der Halbleiterindustrie verstanden. Meist wird dieser als geistiges Eigentum des Entwicklers weiter an andere IC-Designer lizenziert, um ihn in ein anderes, meist größeres, IC-Design zu integrieren. Die verschiedenen Blöcke sind dabei bereits getestet und können wie ein Puzzle zusammengesetzt werden, sodass man vorhandene IC-Strukturen verwenden und nur Teile neu entwerfen muss. Ein Chiplet ist also kein voll funktionsfähiger Einzelchip, sondern ein Teil eines Chips, den man mit anderen Funktionselementen kombinieren kann. Die Konzepte und ersten Implementierungen von Chiplets versprechen nicht nur höhere Integrationsdichten, sondern berühren auch Umwelteigenschaften der Elektronik in Bezug auf Ressourceneffizienz, kritische Rohstoffe, Modularität und Wiederverwendbarkeit von Designblöcken.

Letzte Änderung:

Fraunhofer-Institut für Angewandte Festkörperphysik IAF

Fraunhofer-Institut für Angewandte Festkörperphysik IAF